intro

In that section we will explain cpu stages and how to build a cpu based on the sc_core cpu.

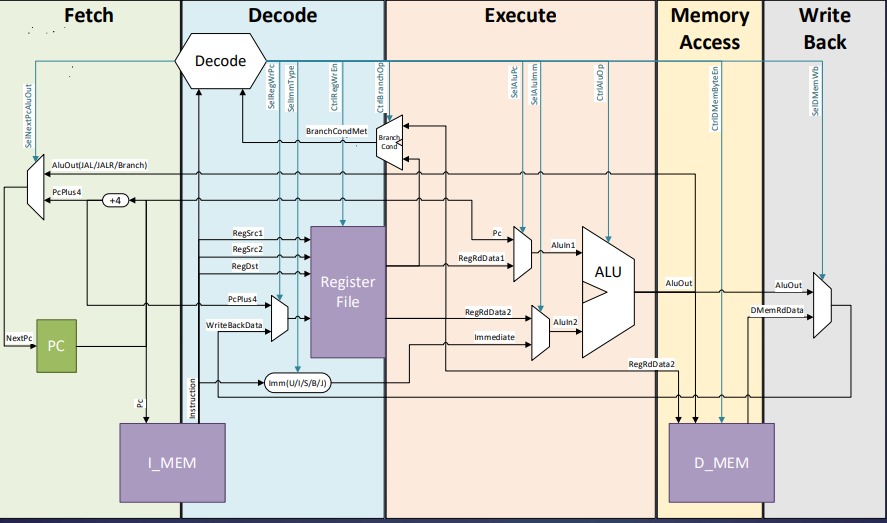

From now on, the following figure will be your "best friend" and will help you understand the cpu stages.

important note:

We suggest taking your time to read and understand everything written here, and don't rush or worry about how long it takes.

This section is extremely helpful for students:

1) Students who are working with Mafia RTL for the first time.

2) Students who are designing a CPU for the first time.

3) Students who want to learn Mafia RTL coding style.

4) Students who want to get better at System Verilog.

5) Students who want to promote to MAFIA project by doing their B.Sc. project.

After you finish reading this section we suggest you to write your own cpu core based on the sc_core cpu.

We will be more than happy to help you with that.

sc_core files

The main file, called the sc_core.sv, is made without any levels of hierarchy means that it has no module instantiations.

We also have two more files: one is called macros.sv, which has some macros like flip-flops. The second file is named sc_cpre_pkg.sv, and it has some parameters and typedef enumerators as part of our coding style.