SW Compilation

In this section we will write a basic C program and compile the software part of the project.

- Go to

verif/mini_core/testsand create file namedbasics.cwith the following content:

int main(){

int x = 1;

int y = 2;

int z = x + y;

return 0;

}

- Type the following command in the terminal to compile the C program we just wrote:

./build.py -dut mini_core -test basics -app

- Go to

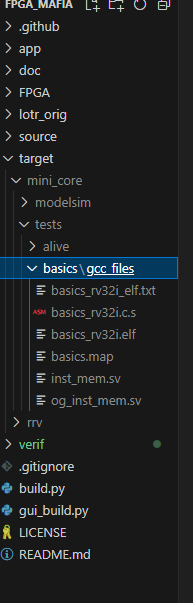

target/mini_core/tests/basicsand observe the content of the folder. You should see the following files:

WOW we got all the files we need to run the HW simulation. Let's try to understand what each file is doing: (those are the most important files)

basics_rv32i.c.s- This is an assembly file that was generated by the compiler. This file contains the assembly code of the C program we wrote.basics_rv32i.elf- This is an ELF file that was generated by the compiler. This file contains the machine code of the C program we wrote. This file is not readable by humans so we wont use it at this point.basics_rv32i_elf.txe- This is the converted version of the ELF file written in assembly code. This file is readable and we will use it allot while running and debugging the HW simulation.inst_mem.sv- This is the instruction memory file that contains the machine code of the C program we wrote suitable for

RISC-V ISA.

Hey, doesn't this seem like something we've seen before? Yes, you're correct. We did something similar when we were compiling a C program in the RISC-V GCC section in TFM. But now, the difference is that we're connecting everything to the MAFIA environment and doing it in a more automated way.

note: Please download the riscv-spec cause you will need it in the future.

Please make sure you understand RV32I Base Instruction Set as shown in chapter 19 and RISC-V Assembly Programmer’s Handbook as shown in chapter 20 cause we will use the following table in the future:

| Register | ABI name | Description |

|---|---|---|

| x0 | zero | Hard-wired zero |

| x1 | ra | Return address |

| x2 | sp | Stack pointer |

| x3 | gp | Global pointer |

| x4 | tp | Thread pointer |

| x5 | t0 | Temporary/alternate link register |

| x6-7 | t1-2 | Temporaries |

| x8 | s0 | Saved register |

| x9 | s1 | Saved register |

| x10-11 | a0-1 | Function arguments/return values |

| x12-17 | a2-7 | Function arguments |

| x18-27 | s2-s11 | Saved registers |

| x28-31 | t3-6 | Temporaries |

Background of SW Compilation command

In this section, we will outline the commands that run in the background when you use the

./build.py -dut mini_core -test basics -app command.

mkdir ./target/mini_core/tests/basics

mkdir ./target/mini_core/tests/basics/gcc_files

cd ./target/mini_core/tests/basics/gcc_files

riscv-none-embed-gcc.exe -S -ffreestanding -march=rv32i -I ../../../../../app/defines ../../../../.././verif/mini_core/tests/basics.c -o basics_rv32i.c.s

riscv-none-embed-gcc.exe -O3 -march=rv32i -T ../../../../../app/link.common.ld -I ../../../../../app/defines -Wl,--defsym=I_MEM_OFFSET=0 -Wl,--defsym=I_MEM_LENGTH=65536 -Wl,--defsym=D_MEM_OFFSET=65536 -Wl,--defsym=D_MEM_LENGTH=61440 -nostartfiles -D__riscv__ -Wl,-Map=basics.map ../../../../../app/crt0_default.S basics_rv32i.c.s -o basics_rv32i.elf

riscv-none-embed-objdump.exe -gd basics_rv32i.elf > basics_rv32i_elf.txt

riscv-none-embed-objcopy.exe --srec-len 1 --output-target=verilog basics_rv32i.elf inst_mem.sv

cd C:/workspace/fpga_mafia